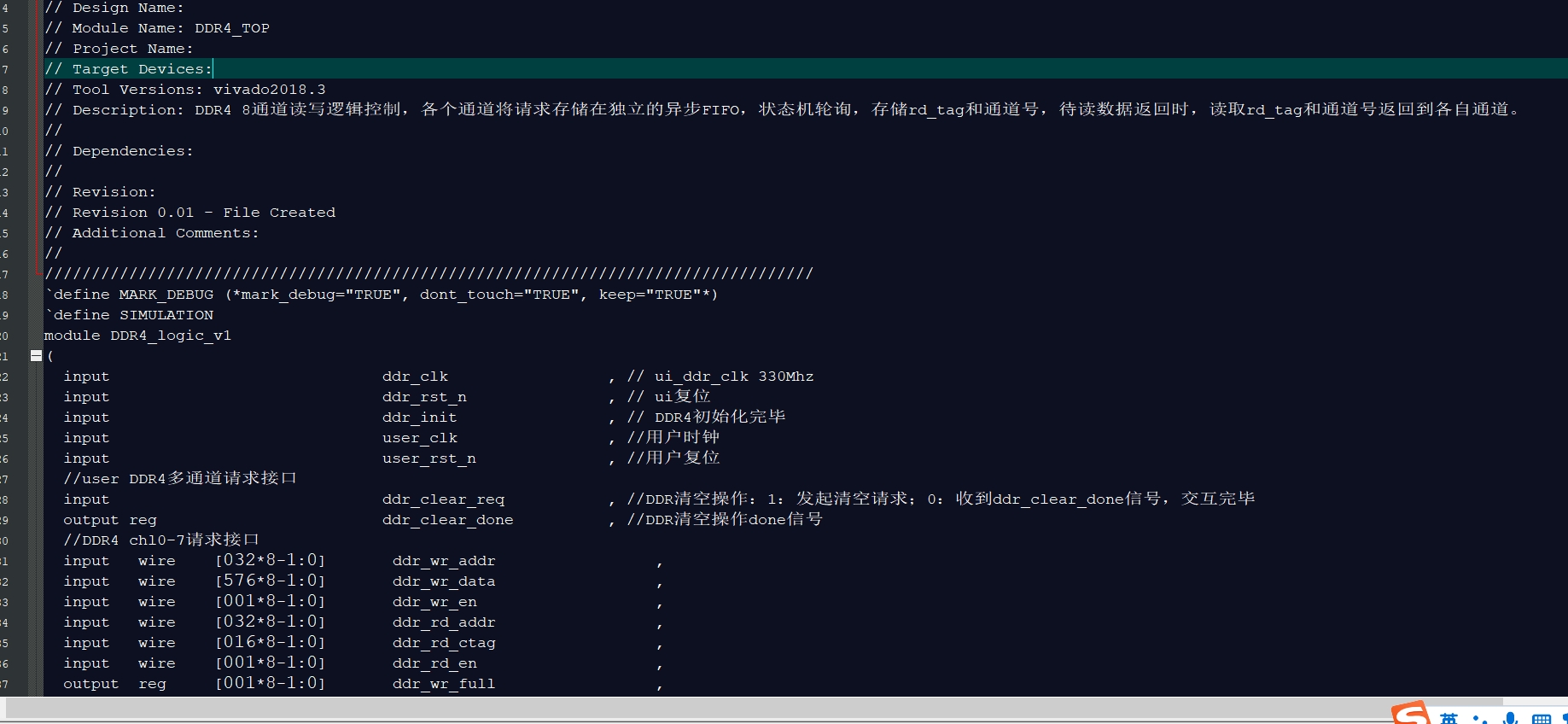

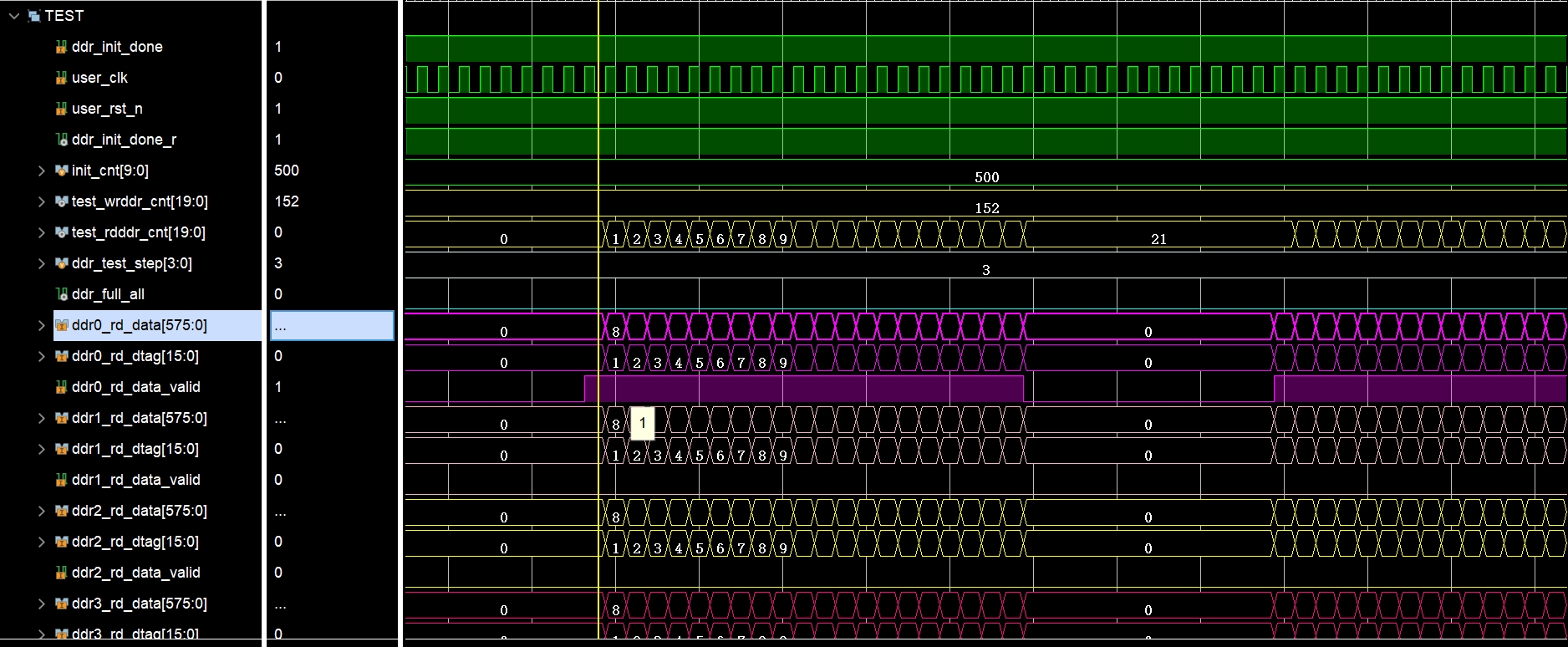

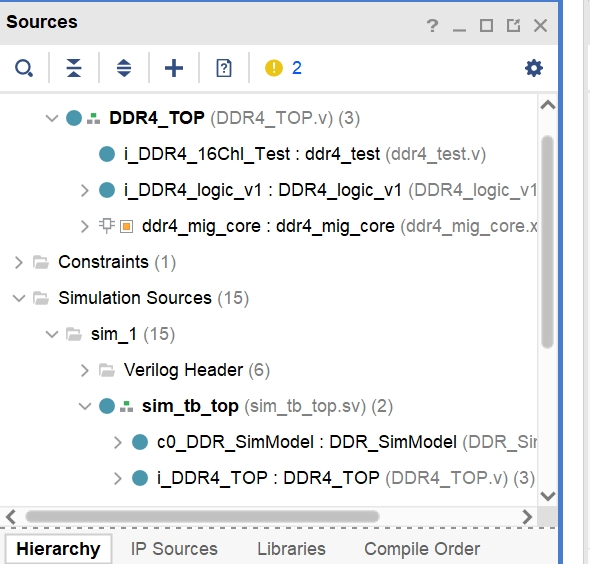

Xilinx DDR4/DDR3 多通道读写防冲突设计,可实现最高8个通道同时读写DDR且不冲突问题,通道数可根据使用来决定。

每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求。

此工程经过2个月的实际上板疲劳测试,功能稳定,时序健壮,性能优异,有需要用到DDR4/DDR3的多通道/单通道的地方,此工程代码可直接移植。

本工程通过Vivado实现,程序中包含详细注释,另赠送一份详细设计说明文档,保证可以弄懂DDR的逻辑和设计架构,可直接应用于工程设计中。

ID:93300674731967969 平芜尽处是春山

平芜尽处是春山