基于fpga的tcp乱序重排算法实现,通过verilog实现适用于fpga的tcp乱序重排算法,并通过实际数据测试验证。

代码里包含注释,可以明白每个模块的含义。

采用自创的乱序重排算法,易于在硬件中实现。

该算法和工程可用于实际应用、算法设计、研究学习。

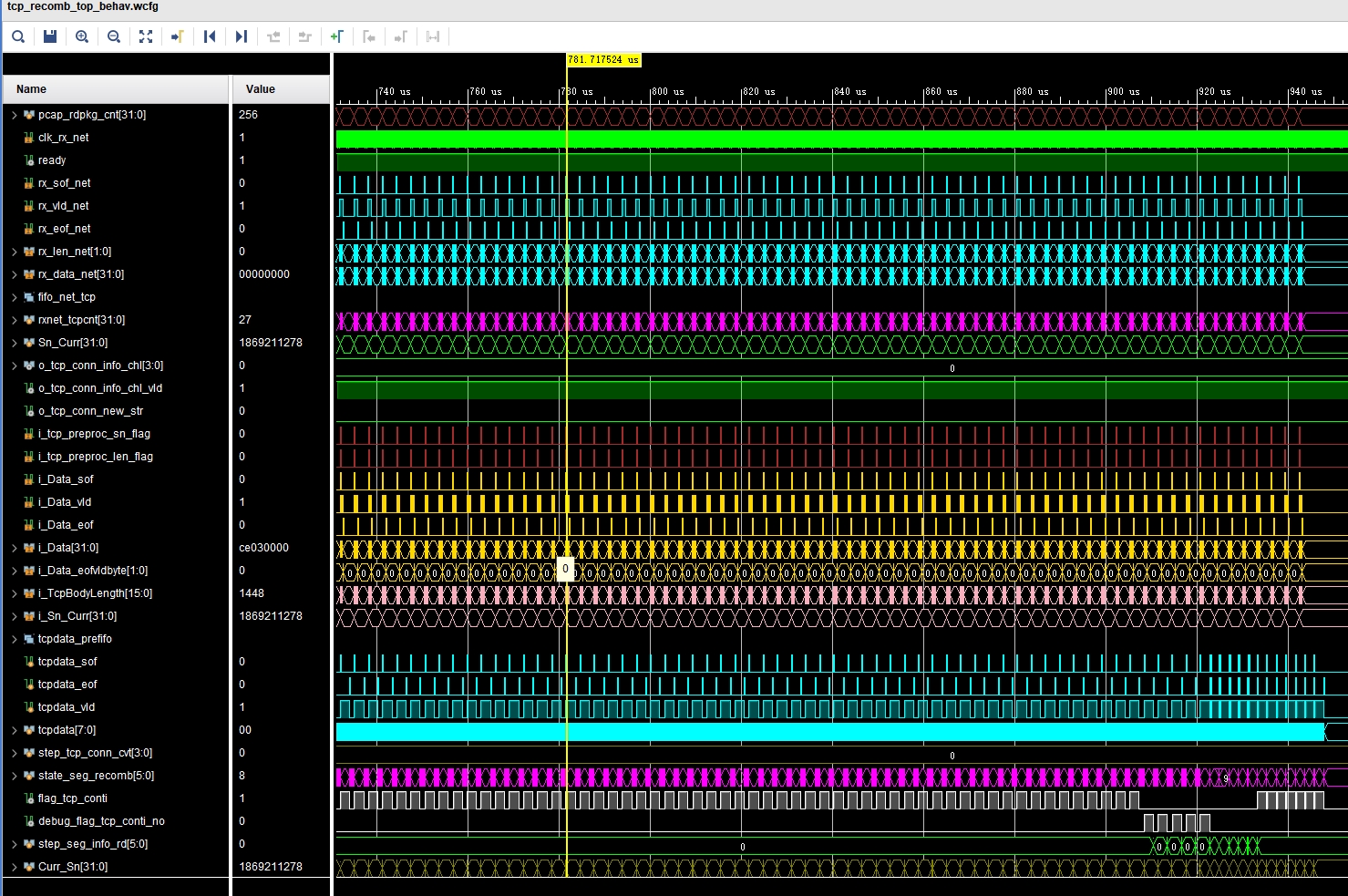

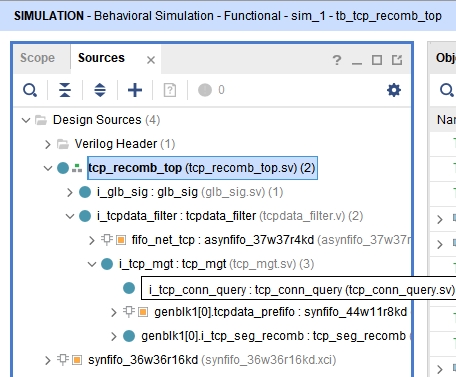

提供测试用的抓包文件,仿真结果。

解决棘手的fpga处理tcp乱序问题。

此工程在实际场景中多次测试,结果正确,性能良好。

可实现tcp的快速重排与恢复。

具有很强的实际意义和算法意义。

YID:87900679350854662 平芜尽处是春山

平芜尽处是春山